摘 要:本文利用Altera公司的FPGA和EDA工具MAX+plusⅡ和实现了基本的边界扫描结构电路,利用此设计可以满足数字电路系统可测性设计和在系统配置(In-System Configuration)的要求。

关键词:边界扫描 ;现场可编程门阵列 ;可测性设计

引言

芯片封装技术的发展,特别是表面贴装技术(SMT)的发展给传统针床测试带来很多困难。为了解决传统测试方法中存在的物理探针不可达等问题,联合测试行动小组(JTAG)提出了边界扫描体系结构,后来成为IEEE1149.1标准。利用边界扫描技术,可以对大规模数字集成电路芯片、多芯片模块和由数字集成电路芯片组成的印制电路板进行测试。边界扫描体系结构的可扩展性也使得边界扫描技术得到了很大的扩充,出现了包括IEEE1149.4、IEEE1149.5、IEEE1149.6在内的新的测试标准。同时,许多器件厂商也扩展了它的功能,使其支持在系统配置,成为IEEE1532标准。

1 边界扫描的基本结构

2 TAP控制器仿真图

边界扫描的基本结构

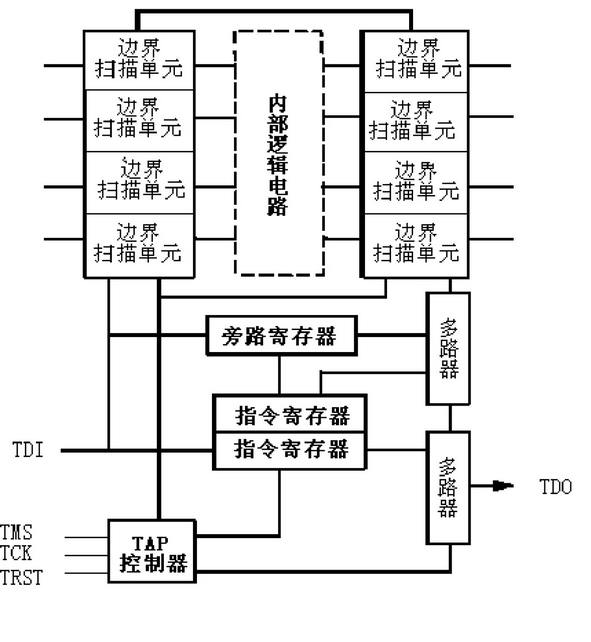

根据IEEE1149.1标准,边界扫描的基本结构如图1所示,包括以下几个部分:

测试访问接口(TAP):包含TDI(测试数据输入)、TDO(测试数据输出)、TMS(测试方式选择)和TCK(测试时钟)4个必须的信号引脚,以及一个可选的信号引脚TRST(测试复位),所有边界扫描操作均通过上述5个信号进行控制;

TAP控制器:接收TMS和TCK信号,控制TDI到TDO的测试数据通过的路径,并控制各寄存器按要求捕获或更新数据;

指令寄存器:锁存当前操作的指令代码;

边界扫描寄存器:器件的每一个输入、输出引脚都有一个边界扫描单元(BSC:Boundary Scan Cell)用于锁存输入信号或者施加预定的信号;

旁路寄存器:可将边界扫描寄存器旁路,直接将TDI的输入数据传到TDO口输出。

除上述单元外,边界扫描结构还可以包括器件厂商自己定义的用于实现其他功能的数据寄存器,比如器件标识寄存器等。

边界扫描结构在可测试性技术中的应用

边界扫描机制提供了一种完整的、标准化的可测试性设计方法。自从边界扫描标准出现以来,市场上支持边界扫描机制的芯片及设计开发软件与日俱增,其应用越来越广泛,成为了第三代可测试性技术的主流。在利用FPGA进行SoC设计时,整个系统和单独模块的可测试性是必须要考虑的问题,边界扫描结构的可扩展性为其提供了良好的解决方案。为了达到可测试性设计的要求,可以在设计中加入独立的边界扫描结构,插入数据扫描链,这样就可以通过TAP接口方便地进行测试和调试工作。不过,由于FPGA芯片本身的边界扫描结构的功能在芯片生产出来之后就已经确定了,因此设计人员不能按照自己的要求利用该资源,故在设计中加入的边界扫描结构需要自己设计实现,并且需要占用FPGA芯片的资源,这一点是需要注意的。

边界扫描结构的FPGA实现

TAP控制器的设计

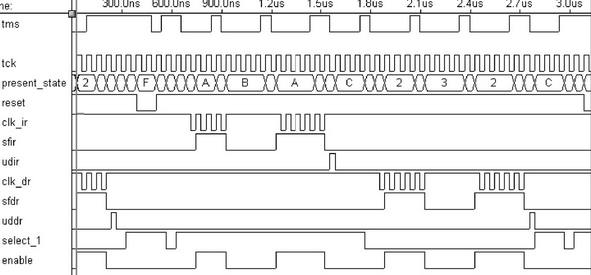

IEEE1149.1标准对于TAP控制器的功能结构作了明确的定义。TAP控制器由TAP状态机和TAP控制信号产生电路两个部分组成。状态机共有16个状态(见表1)。TAP状态机在测试时钟TCK的上升沿根据测试方式选择信号TMS改变状态,同时产生TAP控制信号用于控制数据寄存器(旁路寄存器、器件标识寄存器、边界扫描寄存器等)的动作。TAP控制信号包括:

Reset :边界扫描结构的复位信号;

Select :TDO输出选择信号,控制是测试指令输出还是测试数据输出;

Enable :输出TDO使能信号;

Shift IR :指令寄存器移位使能信号;

Clock IR :指令寄存器移位时钟;

Update IR :指令寄存器单元的数据更新信号;

Shift DR :数据寄存器移位使能信号;

Clock DR :数据寄存器移位时钟;

Update DR :数据寄存器单元的数据更新信号。

根据IEEE1149.1标准可以利用VHDL硬件描述语言来实现TAP控制器状态机的功能。

测试指令集的设计

边界扫描结构的工作方式由测试指令来控制,IEEE1149.1标准中强制定义了以下3条指令:

Bypass指令:选择旁路寄存器在TDI与TDO之间的连接,从而缩短扫描链的长度;

Extest指令:选择BSC链在TDI与TDO之间的连接,同时输出端口上的BSC加载预置的数据,输入端口的BSC获取输入信号;

Sample指令:选择边界扫描单元链在TDI与TDO之间的连接,同时获取当前输入输出端口的数据,保存在BSC中。

除了强制指令以外,还有一些可选的指令,同时器件厂商也可以定义自己的私有指令。在本文的设计中加入了可选指令IDcode用于读出器件标识寄存器内的标识码,各指令的编码如表2所示。

寄存器设计

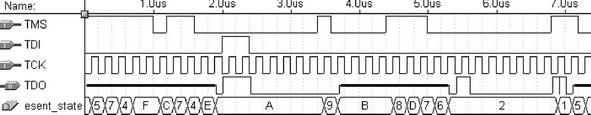

边界扫描中的寄存器包括旁路寄存器、指令寄存器、器件标识寄存器和边界扫描单元寄存器链,这些寄存器可以用通用的移位寄存器实现。本文设计的器件标识代码为10000001,边界扫描单元寄存器的长度为16位,与标准不同的是,这里的边界扫描单元寄存器并没有和器件的输入输出引脚相连。旁路寄存器为D触发器,其它的寄存器长度为8位。在设计中需要注意的是IEEE1149.1要求TDI的数据在TCK上升沿移进,TDO的数据在TCK的下降沿移出,同时数据的最后一位须在Exit1-DR状态移出。

仿真结果

本文在Altera的FLEX10k10 FPGA上实现了上述的基本边界扫描结构,TAP控制器的功能仿真如图2所示,通过接口读出器件标识寄存器里的代码(10000001)过程的时序仿真如图3所示。从图3可以看出,state 处于状态2 时,TDO的数据在TCK的下降沿移出,输出数据为10000001,整个过程满足设计要求。

结语

IEEE1149.1标准定义了一种功能可扩展的边界扫描结构,通过它可以访问和控制芯片内部的数据,从而实现电路测试等功能。随着电子设计技术的发展,SOC的可测性设计必将得到广泛的关注,通过在设计中添加边界扫描结构电路,可以方便地对设计中的关键数据进行监测和对系统进行编程、配置与调试。可以预见,嵌入式边界扫描结构将会在FPGA数字电路设计中得到广泛的应用。