1 POWERQUICC硬件

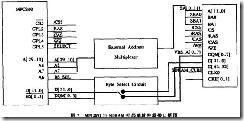

1.1 MPC860存储器接口

MPC860存储管理提供了8个存储器的片选信号,它可以与SRAM、EPROM、FLASHROM、SDRAM、EDORAM以及其他存储器件实现无缝连接。对存储器的存取是通过MPC860内部提供的相应的寄存器和时序RAM对相应接口信号时序进行控制实现的。

MPC860与外接存储器的接口信号有:

①数据总线Data[0:31],32位;

②地址总线Address[0:31],32位;

③控制总线片选/CSO-/CS7,读写R/W,通用控制线GPL-x0~GPL-x5,字节选通线/BS[0-3],迸发指示/BURST,校验收指示DP[0-3]等,总线共享信号/BS,/BR,/BG,AT。

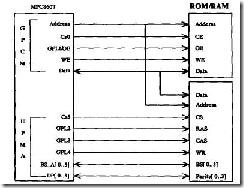

MPC860与外接存储器的接口方式按存储方式分为两类,即GPCM(通用片选机制)和UPM(用户编程机制)。其中地址总线和数据总线是其公共部分,控制总线包括片选信号线(CSx),R/W,BS-Ax,GPL-x以及DPx等。

(1)GPCM (general-purpose chip-select machine)

通用片选机制(GPCM)为那些低速和效率不高的存储芯片提供一种访问方式,它不提供迸发访问机制,因此这种机制通常用于系统BOOT芯片以及那些非迸发性芯片的访问。其数据总线的宽度可以选择8位、16位、32位,下面介绍的FLASHROM采用8位数据总线。

(2)UPMx (user-programmable machines)

用户编程机制支持外部地址仲裁、周期时钟以及实现与DRAM器件真正无缝连接的行列时序的生成。此机制能生成不同的时序满足读、写、迸发读、迸发写等操作。该方式支持32位的数据总线。

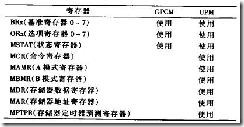

MPC860用于存储控制的寄存器如表所示。所有寄存器都是32位宽。

· BRx,ORx相同下标的BR和OR成对使用,BRx定义相应片选存储器块的起始地址(高16位)、访问方式(GPCM或UPMx)、读写保护方式以及校验与否。ORx定义相应的地址掩码(高16位)、GPCM方式的所有参数。

注意BR0和OR0与其它BRx,ORx不同,其中BR0中的值在系统初始化时与总线上设计的上电配置字有关,OR0中GPCM参数固定只读,正是这些特性决定了CS0上的存储器只能是系统BOOTROM并且硬件设计时序采用GPCM方式。

· MSTAT报告外部存储器校验错以及写保护错。

· MCR在UPM方式的初始化时,读写UPM-RAM的内容。当然也可以用它来仿真UPM方式,这样CPU不但能完成标准的存储器读写以及周期时序,而且能完成特定存储器的操作。例如对SDRAM的操作。

· MDR存放将要写人或从UPMRAM中读出的内容,因此在执行MCR写命令之前,MDR必须预先设置数据。

· MAMR, MBMR:UPMA和UPMB的配置寄存器。包括地址仲裁,各种周期序等。其中16-18位GOCLX[0..2]表示在UPM方式中内存RAM字中的GOL和GOH全部使能的情况下,所选输出到/GPLO的地址线定义(与SDRAM的设计选择010,即将A10输出到/GPLO)。

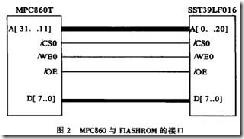

与FLASH接口:

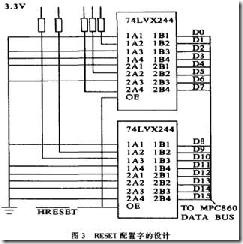

MPC860的GPCM相对于UPM机制无论在硬件接口还是在软件寄存器的编程设置上都简单得多,GPCM方式访问存储器的时序以及接口设计与一般的处理器接口相同,比较容易理解。对GPCM来说其使用的寄存器只有3个,即:BRx、ORx、MSTAT。我们对FLASH MEMORY只需正确设置BR0和OR0中可编程部分,另外根据参数正确设计总线上的RESET配置字。此SST39LF016为2Mbyte,8位数据宽,编址为0x12800000,因此BR0:0x12800401,OR0:0xffe0920,其RESET配置字设计如图。

当系统复位时,HRESET低2片244开放,MPC860读入总线低16位,对应下表配置字,其中BPS(D4D5)为初始时的总线宽度。

与SDRAM接口(内部地址仲裁):

可以看出MPC860与存储器接口信号的生成,是通过对64个32位RAM字编程以及片选寄存器(BRx和ORx)的正确设置来实现的。RAM的编程较为复杂和烦琐,可以用工具软件根据需要生成所需数据。

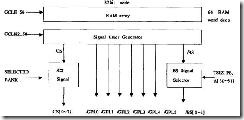

现在市场上性能价格比好的内存条有168线的EDORAM以及14.4线的SDRAM笔记本内存条,在本设计中我们使用144线的SDRAM。MPC860的GPL2输出行选信号(/RAS),GPL3输出列选信号( /CAS) , MPC860地址线(A18一A29)在使用内部仲裁逻辑时是复用的,高端地址线A9一A20作为行地址在RAS有效时复用在A18,/GPLo, A20-A29上,这种复用关系由MxMR中的Amx (001)所设置的,当然行列值不同的内存该设置不同,而复用与否由ORx [SAM]位(为0不复用,1复用)以及内存字[AMX]位决定。这里我们注意A19被/GPLO所替代,在行地址仲裁时,/GPLO由MxMR的GOCLX[0..2]位决定执行哪一条地址线的时序。本设计中内存大小为64M ,12行9列,接口连接见图。片选线选CS5,内存基址为0x00000000,因此设置如下:

OR5 = 0x00000A00 (SAM=1内部仲裁,BIH = 0支持迸发(Burst)方式),BR5 = 0x00000081( MS=10 UPMA方式,PS=00 32位,MAMR = 0x9c924111(Amx=001 , A9-A20复用到A18-A29 , GOCIac[0..2]=010 A10->GPL0 )。

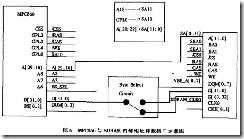

与SDRAM接口(外部地址仲裁):

外部地址仲裁是在MPC860外利用MPC860提供的GPL5引脚实现外部仲裁的地址选择,在这种情况下MPC860的地址线不复用,而是将12行9列共21个地址线分别接到2选1的器件(74ls257 )的a,b端,在行锁定周期选通12个行地址信号,在列锁定周期选通9个列地址信号,这就是GPL5的功能。其它信号与内部地址仲裁相同。